eSPI平台與Super IO的應用簡介

(Intel eSPI platform with Super IO)

2021-06-16

簡介

Intel在2020年推出Tiger Lake系列CPU,並正式移除Low Pin Count Bus(LPC),且整合過去Serial Peripheral Interface(SPI)介面升級為Enhanced Serial Peripheral Interface(eSPI),本文簡述eSPI在開機過程中與平台SoC的行為,以及Super IO可以搭配的產品應用,及問題協助。

Super IO

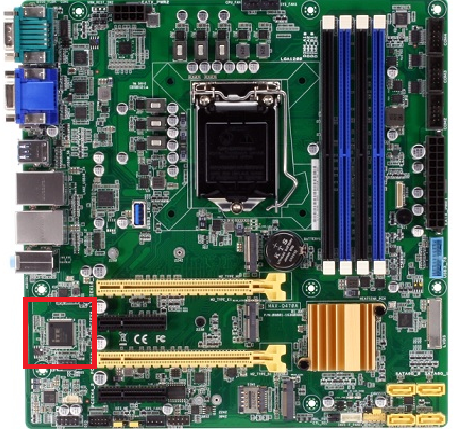

元件整合包含高速UARTs、Intel S0ix、PECI 3.0、5 Fans、5 HWM、PS2,並且為主控系統整體的Power sequence,與CPU之SoC或PCH連接,完整的開發產品如下圖而紅色框框為Super IO

由聯陽半導體推出最新eSPI Super IO包含消費級IT8625與工控級IT8786,目前都已經有eSPI平台的成品經驗,為了能了解Super IO與平台的行為,接著我們簡述一下Super IO,在平台中扮演的角色。

Super IO 功能與特色

產品廣泛的被使用在主機板、工業電腦、一體成型電腦 ( AIO ) 以及工作站的應用上。除了傳統輸出入的功能, 例如全功能序列埠UARTs Support RS-232, RS-422, RS-485、印表機介面 ( Parallel Port )、鍵盤&滑鼠 ( KBC ) 介面、通用型I/O ( GPI/O ) 介面等,還內建硬體監控 ( Hardware Monitor ) 以及機殼開啟偵測等功能。

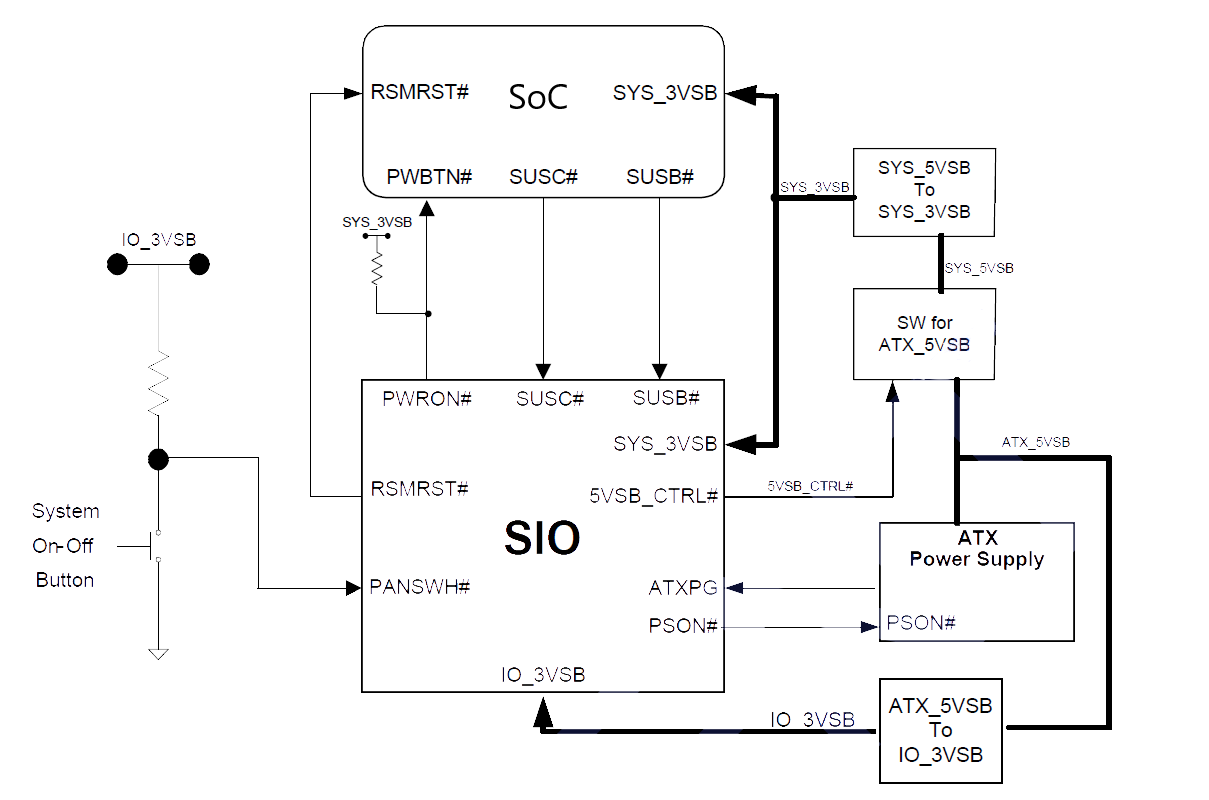

最重要的是Super IO還掌握著整個系統的電源 (Power),也就是時序的控制,下方我們展示了與平台連接的基本架構圖:

1. 當我們按下system On-Off Button

2. SIO端會發送PWRON#

3. SOC拉起SUSC#與SUSB#

4. SIO端會控制PSON#以便啟動整體的Power

5. 最後確認Power供應無虞會將RSMRST#通知SoC Power OK

6. SOC會再向上Reset eSPI訊號

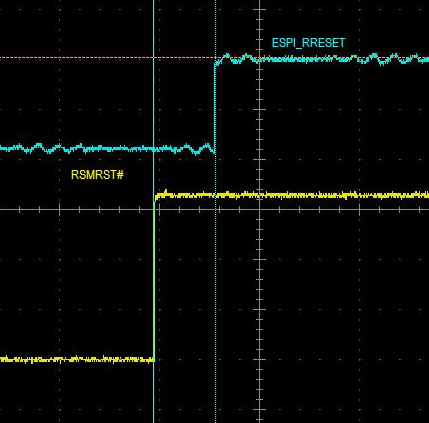

7. 我們就可以在示波器上看到如下圖訊號

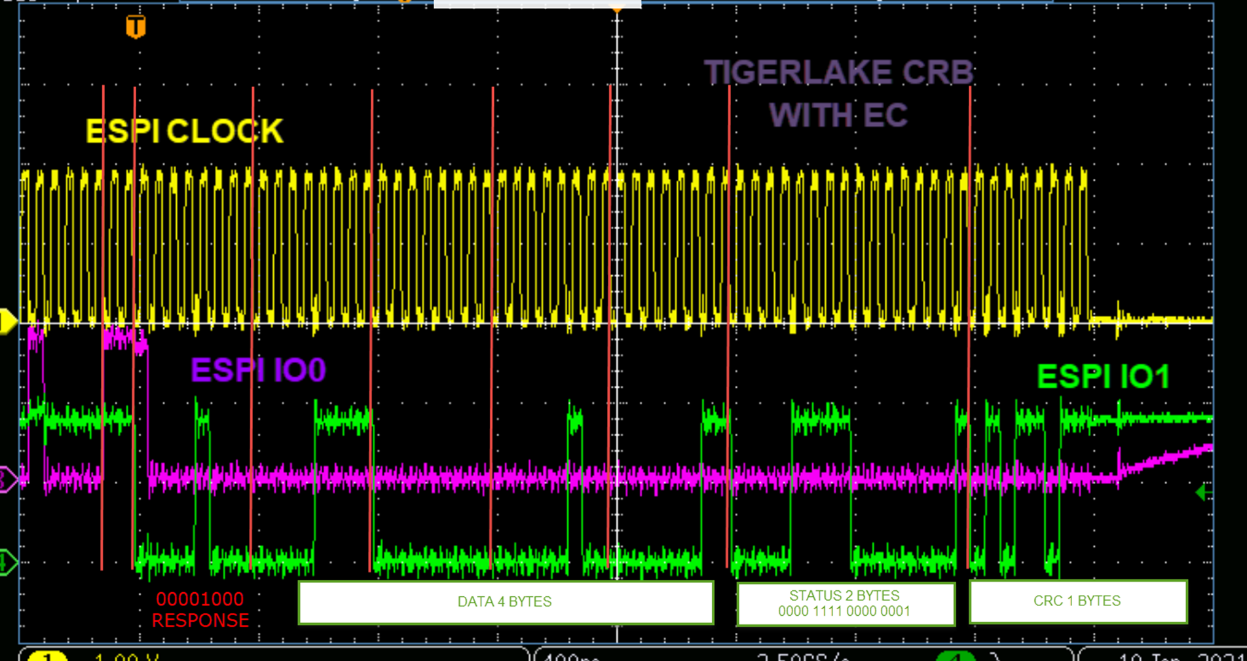

隨後系統就會進入BIOS的啟動程序與eSPI的溝通,可測量到eSPI的Command如下圖

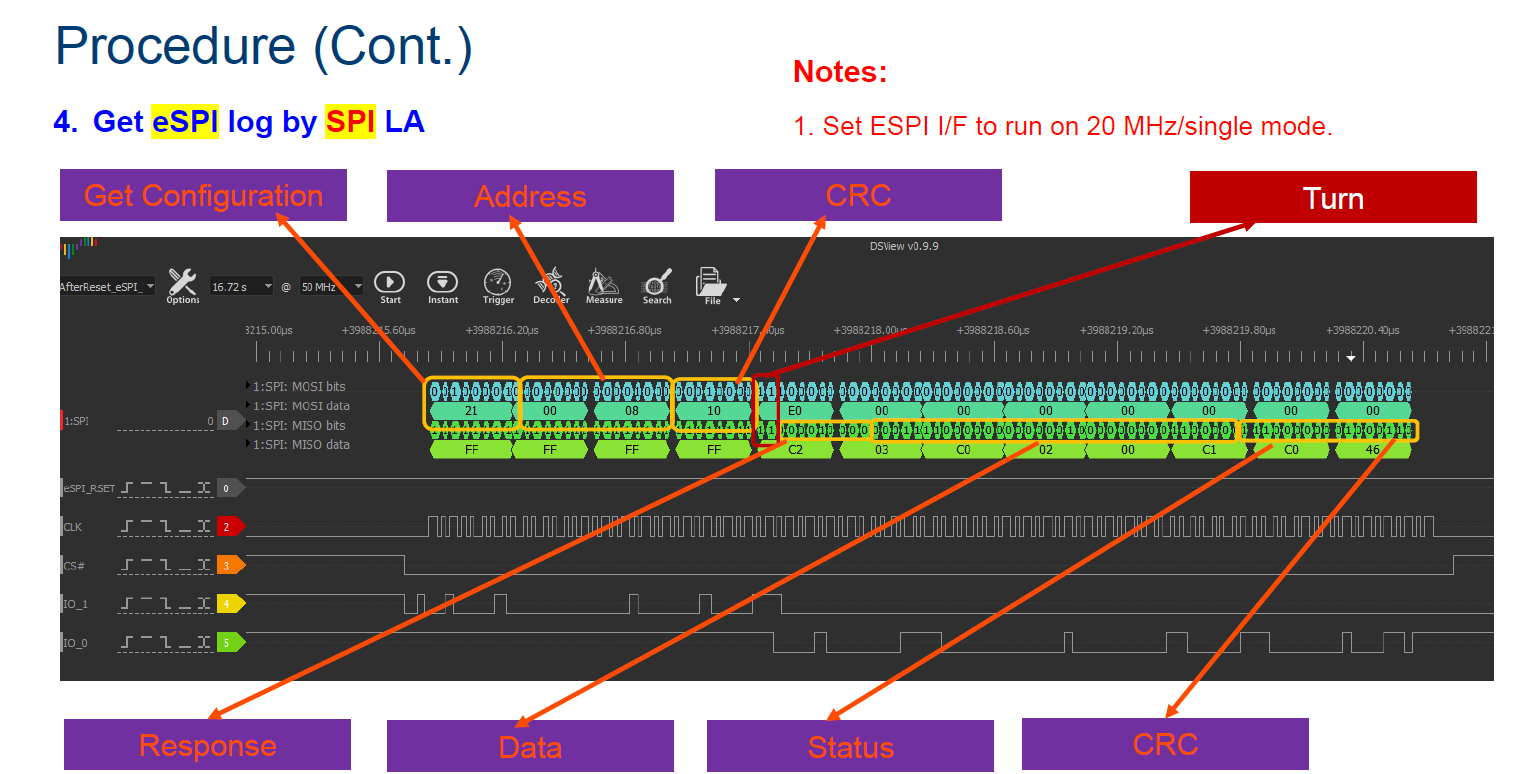

由於eSPI是以封包形式傳送,必須由邏輯分析儀 (LA) 在其中呈現如下圖

細部說明在此就不多加敘述。

結論

需要注意的是eSPI Command並不會多次發送,只要ACK沒有收到,整個系統就會卡住,因此在驗證時一定要確認SIO與PCH之間的每一個環節都不能遺失,並且如果當系統卡住時,可以利用LA解析看看是不是漏了那個ACK,或是時序導致無法正常進入系統,以上就是針對SIO與eSPI平台在開機時的Command關係。

協助

最後推薦由聯陽半導體推出的最新eSPI Super IO包含消費級IT8625與工控級IT8786,整合上述所提到之Super IO功能,設計簡易,並且也可以與BMC連接,不論是Motherboard or Server皆能套用,我們提供線路Review以及後續問題之技術諮詢和問題的Debug協助,利用LA分析工具與eSPI port 80 debug card協助,讓使用著這在開發上不會有困難。

*若想了解更多資訊或有任何疑問,歡迎聯繫以下窗口 : CBGIntelFAE@synnex.com.tw